| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- ACK Polling

- AT24C16A

- booth algorithm

- keynote 사용법

- c

- booth multiplier

- LEC

- 연산 가속기 설계

- C언어

- ISR

- asynchronous fifo

- keynote 도형 회전

- booth multiplier 설계

- ARM

- LinkedList

- Keynote 표

- keynote 도형 복사

- 곱셈기 설계

- lec check

- 자료구조

- 비동기 FIFO 구조

- EEPROM 동작

- FIFO 설계

- Async FIFO

- keynote

- i2c

- cadence conformal eco

- Page Write

- Sync FIFO

- malloc

- Today

- Total

JINTBEAT Design Life

ARM I2C 응용 - EEPROM(ATmel) 동작 분석 본문

Description(AT24C01/02/04/08/16A) : 기본 정보이고, 그냥 한번 스윽 읽어보면 된다.

Features

• Low-voltage and Standard-voltage Operation

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 5.5V)

• Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),

1024 x 8 (8K) or 2048 x 8 (16K)

• Two-wire Serial Interface

• Schmitt Trigger, Filtered Inputs for Noise Suppression

• Bidirectional Data Transfer Protocol

• 100 kHz (1.8V) and 400 kHz (2.7V, 5V) Compatibility

• Write Protect Pin for Hardware Data Protection

• 8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes

• Partial Page Writes Allowed

• Self-timed Write Cycle (5 ms max)

• High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

• Automotive Devices Available

• 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead

SOT23, 8-lead TSSOP and 8-ball dBGA2 Packages

• Die Sales: Wafer Form, Waffle Pack and Bumped Wafers

Pin Configuration

Memory Organization

1. AT24C01A, 1K SERIAL EEPROM : 8byte씩 16page로 구성된다. 1K는 7bit data word address가 필요하다.

2. AT24C02, 2K SERIAL EEPROM : 8byte씩 32page로 구성된다.

3. AT24C04, 4K SERIAL EEPROM : 16byte씩 32page로 구성된다.

4. AT24C08A, 8K SERIAL EEPROM : 16byte씩 64page로 구성된다.

5. AT24C16A, 16K SERIAL EEPROM : 16byte씩 128page로 구성된다.

Device Operation

1. Clock & Data Transitions

SDA pin은 보통 외부 device에 의해 풀업되어 있다. SDA pin을 통한 Data는 SCL이 "LOW"인 구간에만 바뀔 수 있다. SCL이 "HIGH"인 구간에서의 SDA Data 변경은 START & STOP condition을 나타내주는 용도로 쓴다.

2. START 조건

SCL이 "HIGH"인 구간에서 SDA의 falling transition을 나타낸다. 모든 command중에서 가장 우선시 된다.

3. STOP 조건

SCL이 "HIGH"인 구간에서의 rising transition을 나타낸다. STOP 조건은 EEPROM을 standby power mode로 전환시켜준다.

4. ACKNOWLEDGE

모든 주소들과 Data word들은 EEPROM으로 8bit 단위로 직렬로 전송된다. EEPROM은 각각의 word를 전송받았다는 신호를 "zero"를 신호로 전송해준다.

5. STANDBY MODE

AT24C01A/02/04/08A/16A device는 다음 조건에 동작하게 된다.

- Power가 올라간 후

- STOP bit를 전송받은 경우

6. Memory Reset

protocol이 interruption된 후, power loss나 system reset 이후에, 다음의 step들로 memory reset을 시킬 수 있다.

- Clock을 9 cycle 출력해준다.

- SCL이 High인 동안, SDA를 High로 유지시켜준다.

- Start condition을 만들어 준다.

Device Addressing

1K, 2K, 4K, 8K, 16K EEPROM은 모두 8-bit device address word를 요구한다.

위와 같이 device address는 EEPROM device를 구분해주기 위한 주소이다. madatory one과 zero sequence로 구성되어 있고, 이것은 모든 EEPROM device들에 공통이다. 그 다음 3bits가 device를 구분하기 위한 주소인데(A2,A1,A0), 3bits를 다 사용할 수 있는 경우는 1K/2K EEPROM을 사용하는 경우이다.

4K EEPROM에서는 A2와 A1만 사용한다. 그리고 A0는 memory page address bit로 사용된다.

8K EEPROM에서는 A2만 사용되고, 16K EEPROM에서는 device address가 사용되지 않는다.

Device Address compare가 끝나면, EERPOM은 zero를 출력한다(ACK 겠지?). compare가 made되지 않는다면, chip은 standby state로 돌아간다.

- 4K EEPROM에서는 디바이스 4개, 8K EERPOM일 때는 2개, 16K EERPOM에서는 1개면, 최대 저장 용량을 16kbit(2KByte)으로 제한해놓은 듯하다.

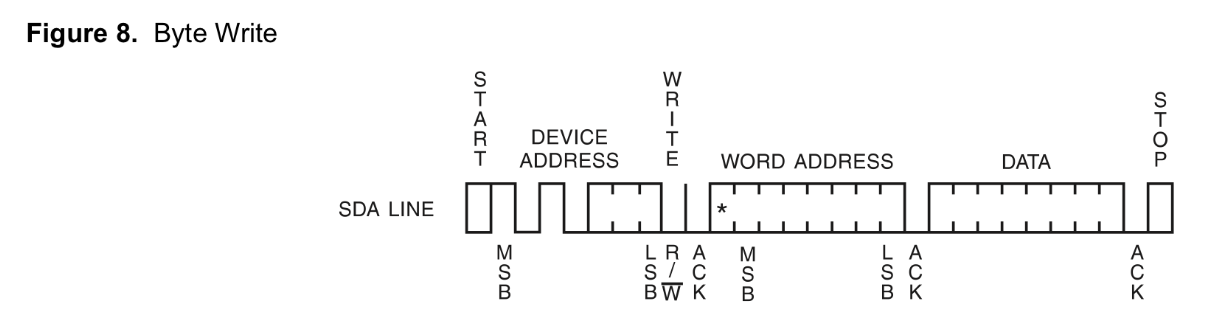

Byte Write

1. START(SCL이 High인 구간에서, SDA의 High to Low Transition)

2. Device Address(MSB to LSB)(Master) + ACK(EEPROM)

3. Word Address(MSB to LSB)(Master) + ACK(EEPROM)

4. Data(MSB to LSB)(Master) + ACK(EEPROM)

5. STOP(stop condition과 함께 write sequence를 종료시켜주어야함)(SCL이 High인 구간에서, SDA의 Low to High Transition)

PAGE WRITE

1K/2K EEPROM은 8byte page write가 가능하고, 4K/8K/16K device들은 16byte page write가 가능하다.

1K라면 2^10bit를 말한다. 그렇다면 2^7 byte를 의미할거다. Address를 8bit data로 전송하니까 2K bit까지는 8bit address로

커버 가능하다는 말이된다. 그런데, 4K부터는 address가 모자라다.

부족한 address분은 Device address LSB들을 땡겨옴을 우리는 Device addressing에서 확인할 수 있었다.

EX ) AT24C04(4K bit, 512byte)의 경우

{A2,A1}으로 device를 구분하고, P0 bit를 가지고 page를 구분함을 알 수 있다.

0~255bit => {1,0,1,0,A2,A1,0,0} , 0~FF 로 표현하고,

256~511 => {1,0,1,0,A2,A1,1,0}, 0~FF로 표현할 수 있음을 알 수 있다.

그럼 page 넘어까지 쭉 incrementally write 할 수 있는가? 그건 또 아니다...

Memory Organization을 확인해보면, 1/2K EEPROM의 경우 8byte, 4/8/16K EEPROM의 경우 16byte로 page의 단위가 정해져 있다. 따라서 memory address write를 할 때, 알아서 증가되는 address의 한계치는 page의 boundary까지이다. spec sheet에는 "roll over"라고 명시되어 있다.

ACKNOWLEDGE POLLING

ACKNOWLEDGE POLLING, Master Device에서 Slave Device인 EEPROM에서 ACK 신호가 나오는지 계속 확인한다는 의미이다.

I2C EEPROM은 Write 동작이 느리다. 내부에서 floating gate에 write 하는데 보통 5ms 정도 걸린다고 한다. 그 동안은 EEPROM이 Busy 상태라서 추가 명령을 받을 수가 없는 것이다. 만약 바로 다시 접근하려고 하면 EEPROM은 NACK(No Acknowledge) 응답을 보낸다.

어떤 방식으로 POLLING할까? Master는 계속 Slave Address를 보내서 ACK가 돌아오는 지 확인한다. EEPROM이 Write 완료가 되면, ACK 응답을 보내준다. 그때부터 다시 정상적인 Read/Write가 가능하게 된다.

대신에 I2C 버스 점유 시간이 늘어난다는 단점이 생긴다.

좀 더 구체적으로 살펴보면, Master가 Start -> Address -> Data 8byte -> STOP 신호 sequence를 마무리하면, EEPROM은 내부적으로 8byte를 Flash에 기록하기 시작한다(Write Cycle 시작), 이때부터 Busy 상태라서, ACK를 보내주지 않게 된다.

Master는 ACK Polling으로 Write Cycle이 끝날 때까지 기다리고, ACK가 돌아오면 다음 Page Write를 시작하게 된다.

Sequential Write의 경우, 같은 Page 안에서만, Master가 Data를 계속 밀어넣을 수 있기 때문에, Stop 조건을 보낸 순간, 내부 Write Cycle이 시작된다. Page 단위로 Stop한 뒤에는, 무조건 ACK Polling이 필요하다.

Random Write(단일 바이트 쓰기)의 경우 한 byte만 써도 EEPROM은 Write cycle을 돌게 된다. 따라서 단일 byte 쓰기 후에도 ACK Polling이 필요하게 된다.

Read Operations : 다른 점은 R/W bit를 1로 set해주는 점이고, 3가지 동작이 존재한다.

1. Current Address Read

EEPROM은 chip power가 유지되는 한, internal data word address counter를 유지하고 있어(Page Write/Sequential R/W, Random W/R 등...) 현재 포인터의 데이터 값을 읽어 올 수 있다. 하지만 지금 포인터가 어디에 있는 지 확실하지 않다면, Random Read(원하는 주소를 W로 1/2 byte써서 지정 후, Repeated START로 Read)로 위치를 잡은 다음 읽는게 정석이라고 한다.

START(Master) -> [DEV_ADDR + R](Master) -> ACK(EEPROM) -> Data Byte(EEPROM) -> Master(NACK : 더 이상 안받겠다는 의미) -> STOP(Master)

하지만 현재 포인터에 의존하면 버그가 숨어들기 쉽기 때문에, Random Read로 먼저 위치를 명시적으로 잡는 패턴을 기본으로 하고, 성능상 필요할 때만 Current Address Read를 쓰는 것을 추천한다. Wrap-Around로 예상치 못한 데이터가 나오는 경우가 있어, 다중 바이트 읽기 시 길이 체크는 필수이다.

2. Random Address Read

Random한 Address에 저장되어 있는 값을 읽어오는 동작으로, data word address를 load하기 위해 "Dummy" byte를 write하는 과정이 필요하다.

device address + data word address를 써주고, EEPROM으로부터 ACK를 받은 후에, 다시 START sequence를 시작하게 되면,

해당 address의 data를 읽어올 수 있게 되고, EEPROM으로 NO ACK 신호를 보내고, STOP 신호를 보내주면 된다.

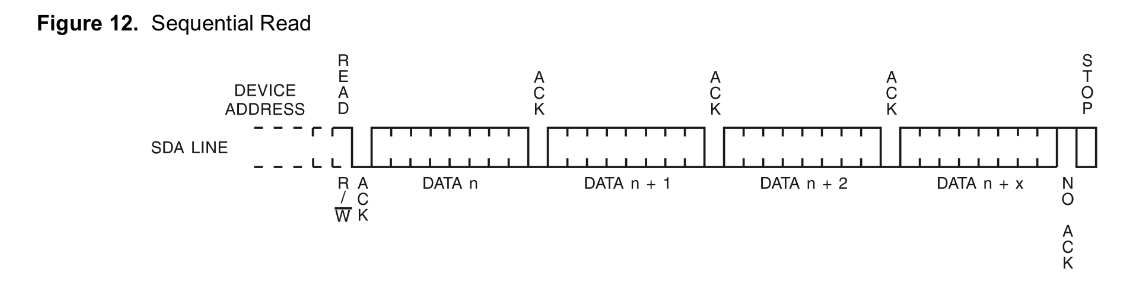

3. Sequential Read

Sequential Read는 current address read나 random address read로 부터 두 경우다 시작시킬 수 있다.

microcontroller가 data word를 받고 난 후, ACK 신호를 보내면, EEPROM은 ACK를 받는 동안, 계속해서 data word address를 증가시켜가면서 data를 출력시켜준다. memory address limit에 도달하면, data word address는 "roll over" 되면서 계속된다.

Master에서 ACK를 주지 않을 때까지 연속해서 동작시킬 수 있고, NO ACK + STOP 신호를 만들어주면 해당 동작은 종료된다.

마무우리

ATmel EEPROM Datasheet의 기본 원리부터 상세 동작까지 모두 분석한 것 같다. ARM I2C Master Driver를 분석해서, 회사에서 EEPROM 제어 FW를 짜봐야겠다....ㅎㅎ.

다음은 FLASH control을 위한 SPI 통신에 대해서 정리해보려고 한다!

'🖥️ - ARM' 카테고리의 다른 글

| ARM I2C(Inter-Integrated Circuit) 동작 원리 (7) | 2025.08.10 |

|---|---|

| ARM - UART 정리 (3) | 2025.07.31 |

| ARM porting - DTM register set 동작 정리 (1) | 2025.07.24 |

| ARM cortex-M3 ISR(Interrupt Service Routine) 구현 Code 예제 (2) | 2025.07.22 |

| ARM cortex-M3 ISR(Interrupt Service Routine) 구현 이론 정리(DTM) (6) | 2025.07.22 |